SICP Exercise 3.29

Question

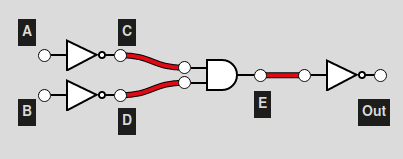

Another way to construct an or-gate is as a compound digital logic device, built

from and-gates and inverters. Define a procedure or-gate that accomplishes

this. What is the delay time of the or-gate in terms of and-gate-delay and inverter-delay?

Answer

Something like the following works:

(define (or-gate a b output)

(let ((c (make-wire))

(d (make-wire))

(e (make-wire)))

(inverter a c)

(inverter b d)

(and-gate c d e)

(inverter e output)

'ok))

The total delay here will be two inverter-delays and one and-gate-delay.